2025年7月18日、2025年RISC-V中国サミット2日目に行われた「高性能コンピューティング分科会」において、中国国産RISC-V技術企業「芯来科技(Nuclei System Technology)」のマーケティング戦略アシスタントバイスプレジデント、馬越(マー・ユエ)氏は、同社が新たに発表した「RVA23プロファイル」仕様に対応する高性能RISC-VプロセッサIP「UX1030H」について詳細に説明した。馬氏は、このIPが中国国産RISC-V高性能プロセッサの「新たなベンチマーク」構築に貢献すると述べた。

中国を代表する国産RISC-V企業として、芯来科技は2018年の設立以来、ゼロベースでの自主開発により、フルラインのRISC-V CPU IP、サブシステム、SoCソリューションを生み出し、32ビットから64ビットまで、汎用と専用の並行発展をカバーする製品体系を完備している。現在、同社の正式なライセンス顧客は300社以上に上り、累積出荷量は数億個に達している。

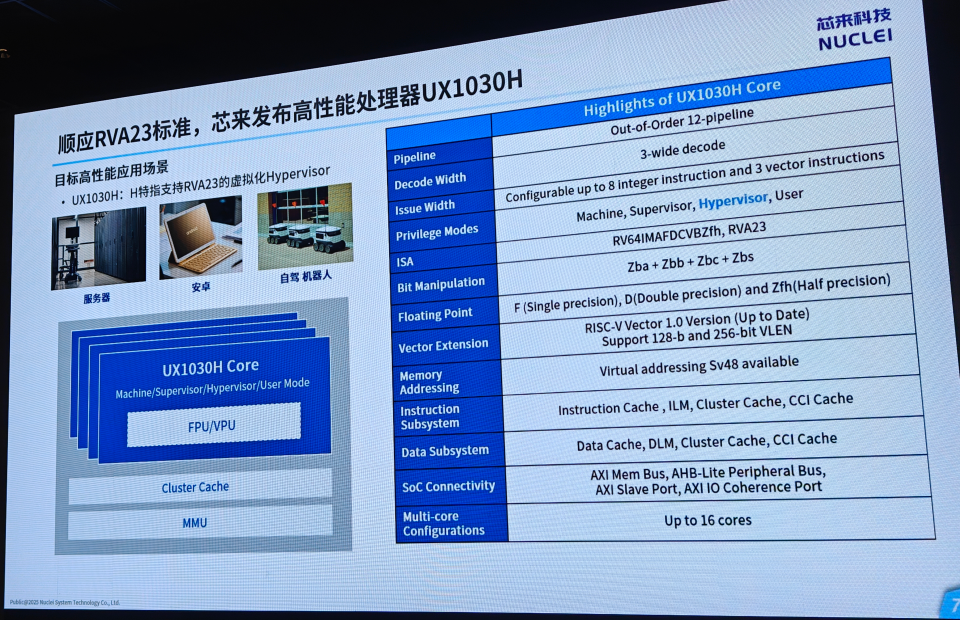

今回の「高性能コンピューティング分科会」で発表された高性能RISC-VプロセッサIP「UX1030H」は、最新の「RVA23プロファイル」仕様をサポートし、仮想化およびベクトル計算拡張をフルサポート。さらに、その上でIOMMUとAIA(Advanced Interrupt Architecture)への対応を追加で提供する。これは次世代の高セキュリティ・高拡張性アプリケーションシナリオに向けたものであり、中国国産RISC-V高性能プロセッサIPのエコシステム統合とシステム適合能力において重要な一歩を踏み出したことを示している。

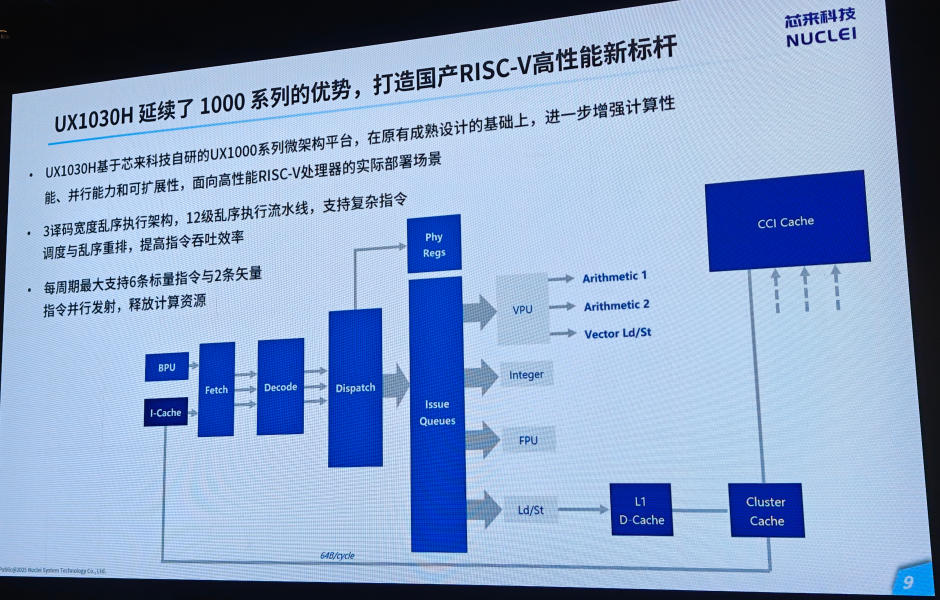

具体的には、UX1030Hは同社独自開発の「UX1000シリーズ」マイクロアーキテクチャプラットフォームを基盤としており、従来の成熟した設計をベースに、計算性能、並列処理能力、拡張性をさらに強化し、高性能RISC-Vプロセッサの実戦的展開シナリオに対応する。このプロセッサは、3デコード幅のアウトオブオーダー実行アーキテクチャを採用し、12段のアウトオブオーダー実行パイプラインを備え、1サイクル当たり最大6本のスカラー命令と2本のベクトル命令のパラレル発出をサポートする。

UX1030Hはさらに「RISC-V Vector 1.0」標準をサポートし、最高256ビット(VLEN=DLEN=256)まで設定可能なベクトル処理能力を備える。これはAI推論、画像処理、信号解析などの計算集約型シナリオに適している。

メモリに関しては、UX1030HはL1命令キャッシュ/データキャッシュ(I/D Cache)、オンチップ命令ローカルメモリ/データローカルメモリ(ILM/DLM)構成、クラスタキャッシュ(Cluster Cache)をサポートする。

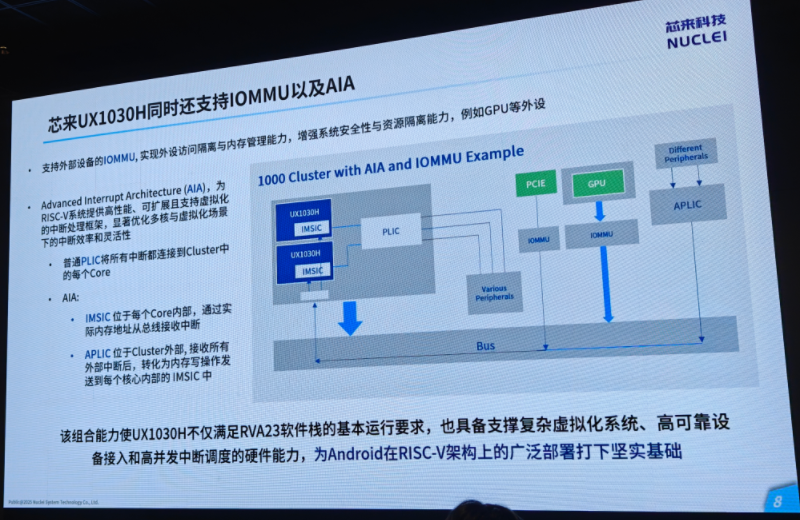

UX1030Hは最新のRVA23プロファイル仕様のサポートに加え、追加でIOMMUとAIAへの対応を提供する。IOMMUサポートは、周辺機器アクセスの分離とメモリ管理能力を実現し、システムのセキュリティとリソース分離能力を強化する。AIAサポートは、RISC-Vシステムに高性能で拡張性があり、仮想化をサポートする割り込み処理フレームワークを提供し、マルチコアおよび仮想化環境下における割り込み効率と柔軟性を大幅に最適化する。

これにより、UX1030HはRVA23ソフトウェアスタックの基本動作要件を満たすだけでなく、複雑な仮想化システム、高信頼性デバイス接続、高並列割り込みスケジューリングを支えるハードウェア能力を備えており、AndroidのRISC-Vアーキテクチャへの広範な展開のための強固な基盤を築いている。

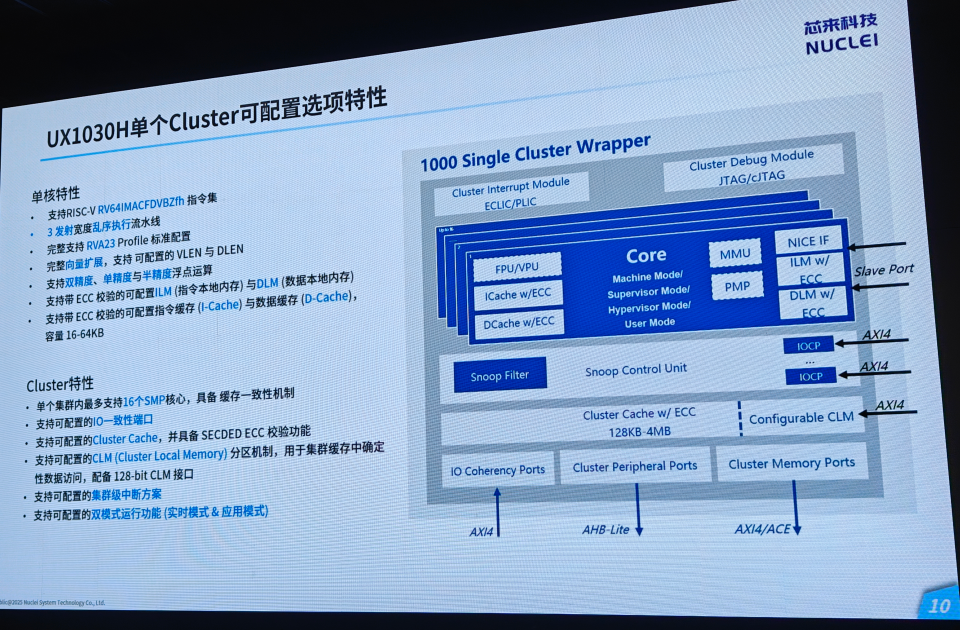

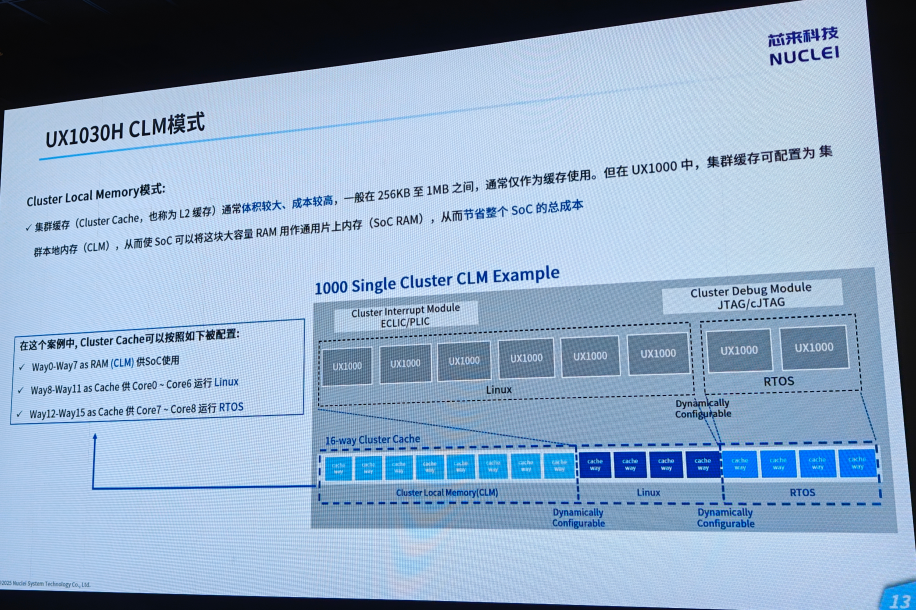

さらに、UX1030Hはマルチコア拡張アーキテクチャをサポートする。単一クラスタ(Cluster)には最大16コアまで設定可能で、設定可能なI/Oコヒーレンシインターフェース、設定可能なクラスタキャッシュをサポートする。クラスタキャッシュは「Cluster Local Memory (CLM)」として構成可能で、CLMインターフェースを提供し、クラスタ内の複数コアや他の計算モジュールによる共有アクセスを可能とする。これは高並行処理・高スループットシステム向けのクラスタ化された展開ニーズに適している。この設計は、データセンターアクセラレータカード、インテリジェント自動車コントローラー、高性能エッジプラットフォームなどへのプロセッサ統合のための信頼性の高い基盤を提供する。

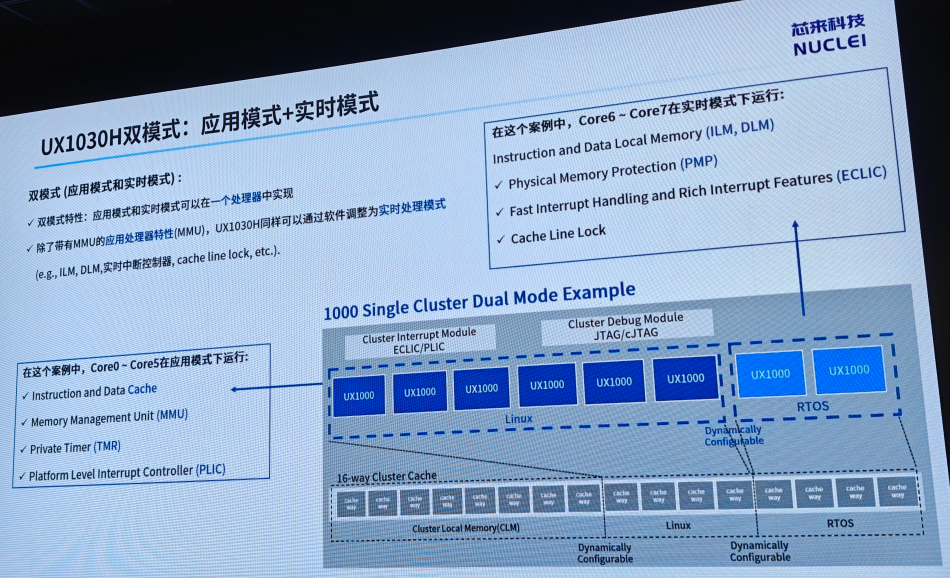

UX1030Hはさらに、Linuxなどの汎用OS動作モードとリアルタイム処理モードのデュアルモード実行構成をサポートする。異なるアプリケーションシナリオに応じてプロセッサ特性を柔軟に切り替え、制御系タスクの低遅延応答要求を満たしつつ、フルOSおよびアプリケーションソフトウェアスタックにも適合する。スマートエッジ、産業制御、車載コンピューティングなど、多様なシナリオに適用可能だ。

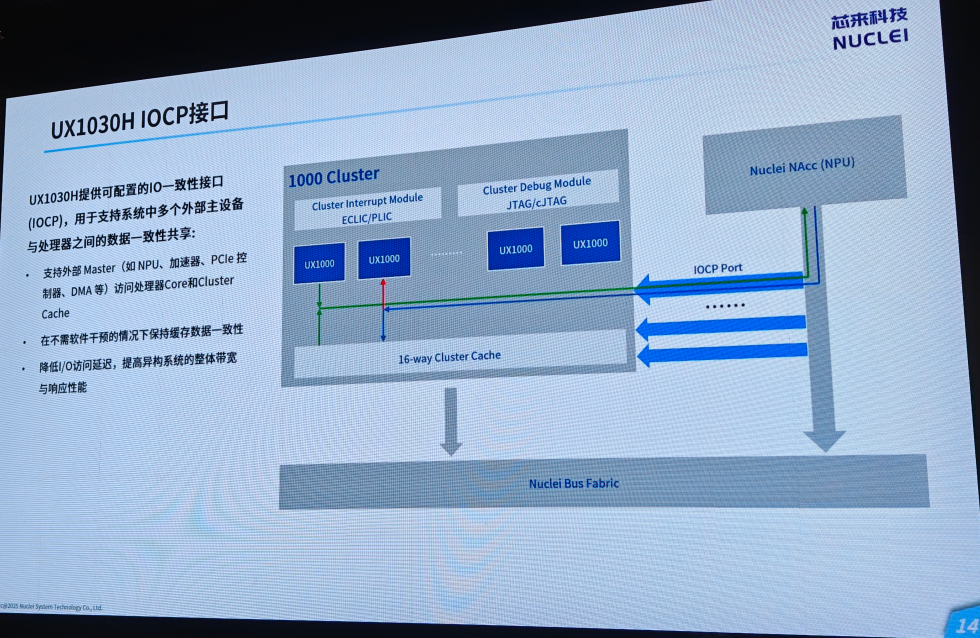

UX1030Hはまた、設定可能なI/Oコヒーレンシインターフェース(IOCP)を提供する。これは、システム内の複数の外部マスターデバイス(NPU、アクセラレーター、PCIeコントローラー、DMAなど)とプロセッサ間でのデータの一貫性を保った共有をサポートするために用いられる:外部マスターがプロセッサコアやクラスタキャッシュにアクセス可能にする;ソフトウェアの介入を必要とせずにキャッシュデータの一貫性を維持する;I/Oアクセスの遅延を低減し、ヘテロジニアスシステム全体の帯域幅と応答性能を向上させる。

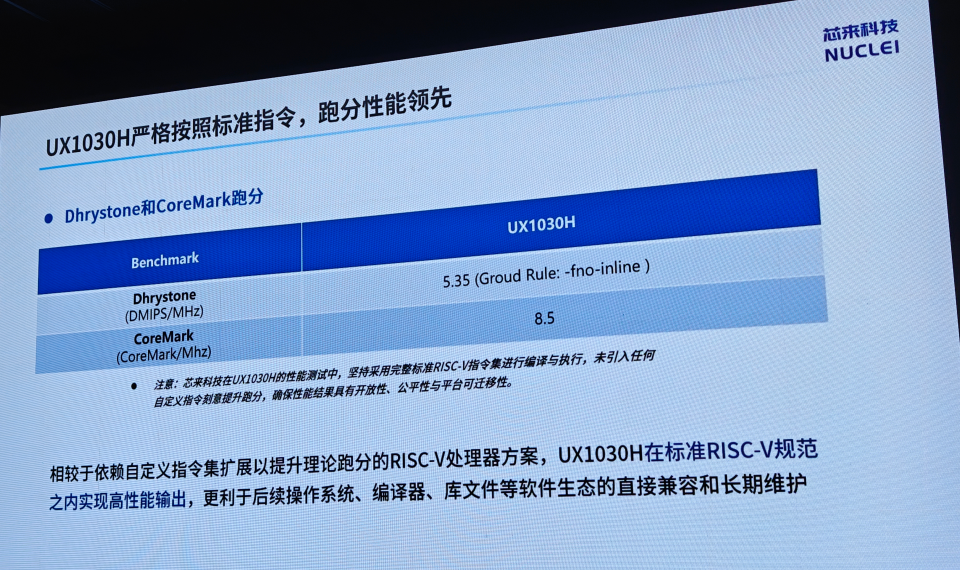

具体的な性能に関して、芯来科技のマーケティング戦略アシスタントバイスプレジデント、馬越氏の説明によると、UX1030HはDhrystone Ground Ruleに準拠し、インライン最適化を無効(コンパイルオプション -fno-inline)とした条件下で、Dhrystoneスコアは5.35 DMIPS/MHzを達成。CoreMarkスコアは8.5 CoreMark /MHzに達した。

馬氏は、このレベルは同クラスのRISC-V高性能コアの中でもトップクラスにあり、UX1030Hの命令スケジューリング、実行パス、キャッシュ体系、パイプラインの深さ設計における総合的な最適化能力を十分に示していると指摘した。理論上のベンチマークスコア向上のためにカスタム命令セット拡張に依存する一部のRISC-Vプロセッサソリューションと比較して、UX1030Hは標準RISC-V仕様の範囲内で高性能を実現しており、後続のOS、コンパイラ、ライブラリファイルなどのソフトウェアエコシステムとの直接的な互換性と長期的な保守性を高めている。

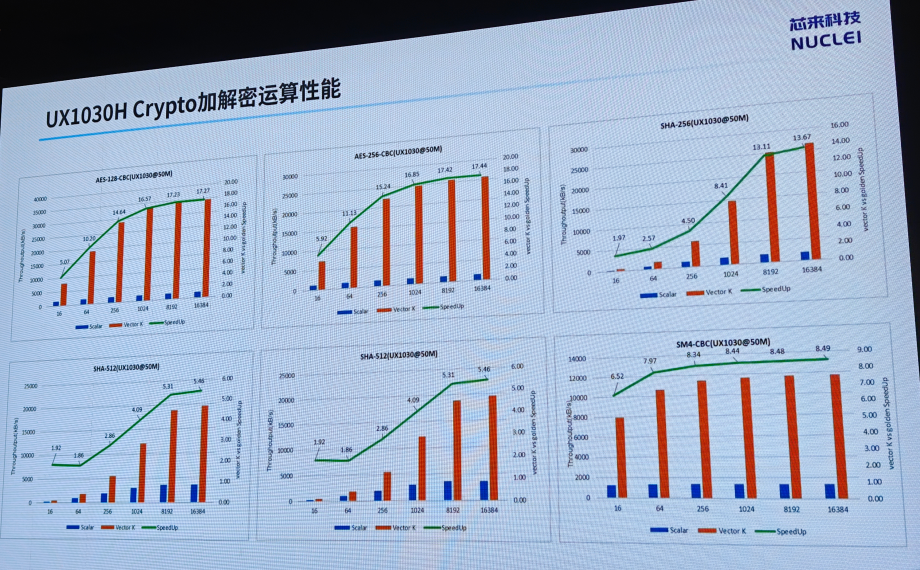

同時に、UX1030Hに内蔵されたVPU(ベクトル処理ユニット)は、画像計算、テンソル演算、暗号化などのワークロードにおいて顕著な性能加速能力を提供する。芯来科技が公開したデータによれば、UX1030Hはベクトル演算性能と暗号化/復号(Crypto)性能の両方で大幅な向上を示している。

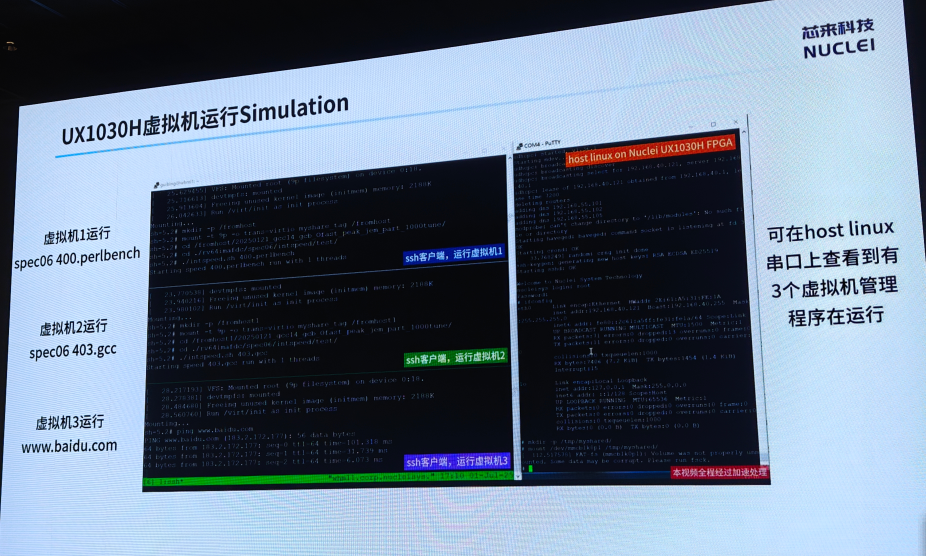

UX1030Hの仮想マシン(VM)実行性能も非常に優れている。馬氏は会場で、UX1030Hが3つの仮想マシンを同時に実行するシミュレーションの様子をデモンストレーションした。

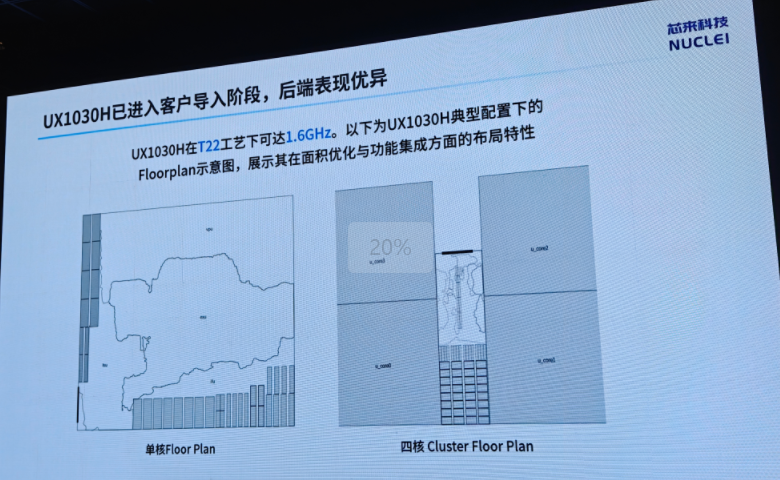

馬氏によると、UX1030Hは現在、顧客導入フェーズに入っており、複数の共同プロジェクトでSoC統合検証とプラットフォーム適応が進行中だという。T22プロセスでは1.6GHzを達成可能である。下図はUX1030Hの典型的な構成におけるフロアプラン図であり、面積最適化と機能統合におけるレイアウト特性を示している。

馬氏は、UX1030Hの発表が、芯来科技のRISC-V CPU IP製品ラインにおけるハイエンド戦略をさらに強化し、国産自律IPの供給力を高め、ソフトウェアエコシステムの汎用コンピューティングプラットフォームへの迅速な移行を支援すると指摘した。また、今後も芯来科技は、汎用処理、インテリジェントコンピューティング、セキュリティ分離、仮想化などの方向性で製品の進化を推進し、より完全で深みのあるRISC-Vプロセッサエコシステムを構築し、国内コンピューティングプラットフォームの高性能化を継続的に推進していく方針だ。

(原文:https://www.icsmart.cn/94239/)