韓国半導体技術者協会が発表した『半導体技術ロードマップ2026』によると、世界の半導体産業は今後15年間で、先進ロジックプロセスを現在の2nmノードから段階的に発展させ、2040年には0.2nmを実現し、1オングストローム(Å)時代に突入する計画である。トランジスタの線幅微細化が物理的限界に近づくにつれ、将来のプロセス進化はリソグラフィー技術のみに依存するのではなく、構造、材料、システムレベルにおける全面的な革新へと軸足を移していく。

2040年以降は1オングストローム時代に、EUVには限界が訪れる可能性

タイムラインから見ると、ロードマップは2025年末頃に半導体プロセスが2nm時代に入り、2031年前後に1nmレベルへ進み、2040年にはロジック回路の線幅がさらに0.2nmまで縮小されると予測している。0.75NA EUV露光装置は2030年前後により微細な線幅をもたらす可能性があるが、リソグラフィーに基づく物理的微細化は次第に飽和に向かい、プロセス競争の焦点は必然的にチップアーキテクチャとシステム全体の設計へと移行する。

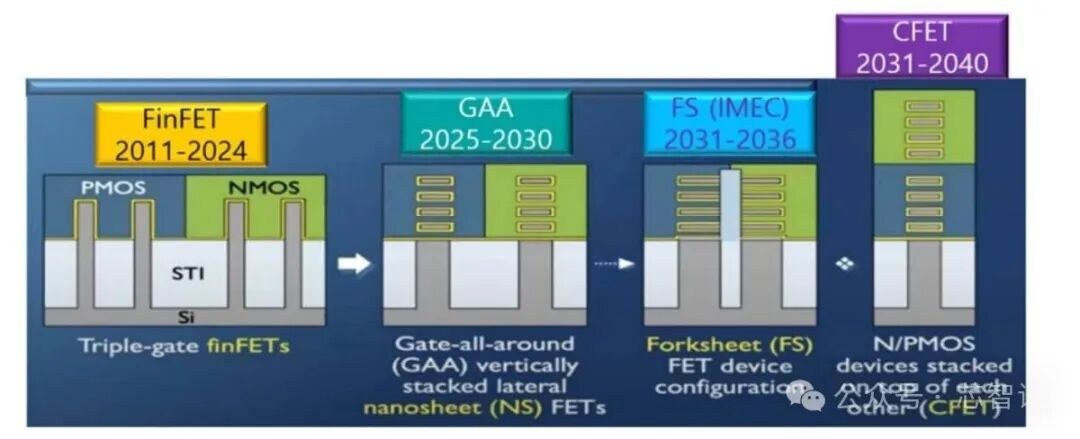

トランジスタは立体化へ

ムーアの法則を継続させるため、ロジック素子はFinFETからGAA(Gate-All-Around)へ移行し、さらにCFET(Complementary FET)などの3次元トランジスタ構造へと進化する。PMOSとNMOSを垂直に積層することで平面密度の限界を突破する。 モノリシック3D(Monolithic 3D)プロセスや、DTCOからSTCO(System-Technology Co-Optimization)への設計思想と相まって、将来の性能向上は個々のプロセスノードの微細化ではなく、全体アーキテクチャの再構築からもたらされる。

メモリも同時に進化:ヘテロ統合と高層数DRAMが鍵に

ロジックプロセスに加え、メモリ技術の進化ペースも0.2nmロジックプロセスと高い同期性を持っている。DRAM分野では、従来のBCATアーキテクチャは7〜8nmで微細化限界に達すると予想され、今後は垂直チャネルトランジスタ、スタック型DRAM、4F²セル、およびHybrid BondingによってCMOS回路を直接メモリアレイと結合するCBA(CMOS Bonded Array)アーキテクチャへと移行し、密度と性能向上を持続させる。

AIアプリケーションの推進しにより、高帯域幅メモリ(HBM)の重要性はさらに高まっている。ロードマップは、HBMがより高い層数での積層、ハイブリッドボンディング、放熱設計を通じて進化し、2031年には20層・8TB/s、2040年には30層以上・128TB/sの帯域幅レベルに達すると予測している。

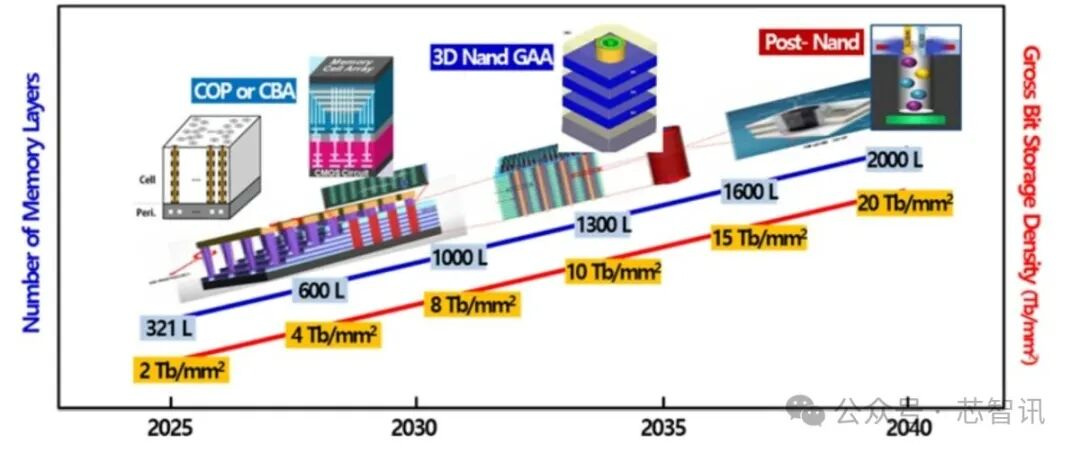

NAND Flashについては、「層数と密度のトレードオフ」という発展経路を進み、321層から、2031年には約1000層、さらに2040年には2000層への挑戦が予想されている。

More than Moore(ムーアの法則を超える)時代へ

半導体産業は、ロジックとメモリの3D化、ハイブリッドボンディング(Hybrid Bonding)、システムレベルアーキテクチャの再構築により、単位面積あたりの集積密度を向上させ、相互接続遅延を低減し、線幅微細化に依存することなく、将来のAIやその他産業が求める高速・低消費電力の要求を満たそうとしている。

(原文:https://www.icsmart.cn/100261/)