韓国メディアの ZDNet Korea が 2 月 24 日に報じたところによると、サムスン電子は最近、中国のメモリチップメーカーである長江存储(YMTC)と、400 層以上の積層型 NAND Flash を開発するために必要な「ハイブリッドボンディング」(Hybrid Bonding)技術の特許ライセンス契約を締結した。それにより、同社の第 10 世代(V10)NAND Flash 製品(430 層)からこの特許技術を使用して製造を行うことになる。

報道によると、サムスンがYMTCから「ハイブリッドボンディング」の特許ライセンスを取得することを選んだ主な理由は、現在、YMTCが「ハイブリッドボンディング」技術において世界をリードしているためだ。また、サムスンは次世代の V10 NAND 以降、YMTCの特許の影響を避けることができなくなると評価した。

3D NAND はなぜ「ハイブリッドボンディング」技術が必要なのか?

従来の NAND Flash の製造では、1 枚のウェハのみを使用しており、NAND アレイと CMOS 回路の集積方法は、CMOS 回路をセルアレイの横に配置する(CMOS Next Array または CAN)方法か、CMOS 回路を NAND アレイの下に配置する(CUA)方法のいずれかだった。

ほとんどの NAND Flash サプライヤーは、最初の 3D NAND プロセスで CAN 方式を採用し、その後のプロセスで CUA アーキテクチャに移行した。マイクロン(Micron)と Solidigm のみが、32 層 3D NAND のロードマップの初期段階で CUA アーキテクチャを採用した。その後、サムスン(Samsung)と SK ハイニックス(SK Hynix)も CUA アーキテクチャに移行し、サムスンはそれを COP(Cell-on-Perry)と呼び、SK ハイニックスは PUC(Cell-Under-Cell)と呼んでいる。

従来の 3D NAND アーキテクチャでは、周辺回路がチップ面積の約 20~30%を占めていた。しかし、3D NAND 技術が 128 層以上に積層されるにつれて、周辺回路が占めるチップ面積は 50%以上に達する可能性があり、これにより記憶密度が低下する。また、この方法では最大 300 層以上の NAND しか収容できず、それ以上の積層では、底部の回路にかかる圧力が回路に損傷を与える恐れがある。

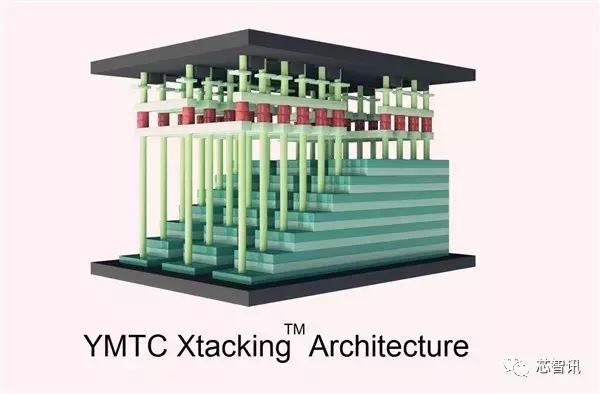

この問題を解決するため、YMTCは早くも 2018 年に新しい Xtacking 技術を発表し、高積層数の 3D NAND の製造を CBA(CMOS Bonded Array)アーキテクチャに転換させることを推進した。

(画像出典:YMTC)

CBA アーキテクチャでは、2 枚の独立したウェハをそれぞれ使用して NAND アレイと周辺の CMOS 論理回路を製造し、その後、CMOS 論理回路を NAND アレイの上に積層する。NAND ウェハと CMOS 回路ウェハは異なる生産ラインで製造できるため、それぞれ最適化されたプロセスノードを使用して個別に生産することができ、生産サイクルを短縮できるだけでなく、製造の複雑さとコストを削減することができる。また、CBA アーキテクチャにより、NAND チップの 1 平方ミリメートル当たりの記憶密度、性能、拡張性をさらに向上させることができる。

CBA アーキテクチャを採用する NAND メーカーにとって、NAND アレイと周辺の CMOS 論理回路をそれぞれ製造するための 2 枚のウェハを完璧に垂直に接続するには、ハイブリッドボンディング技術が不可欠だ。

現在、ハイブリッドボンディング技術は主に 2 種類あり、ウェハ・ツー・ウェハ(Wafer-to-Wafer, W2W)とダイ・ツー・ウェハ(Die-to-Wafer, D2W)。CBA アーキテクチャの NAND は、W2W のハイブリッドボンディング技術に基づいており、従来のチップ接続に必要な「バンプ」(Bump)を省略し、10μm 以下のピッチで接続を形成することができる。これにより、回路パスが短くなり、I/O 密度が大幅に向上し、伝送速度が著しく向上し、消費電力が低減されるだけでなく、チップ内部の機械的応力も低減され、製品の全体的な信頼性が向上する。

また、積層数がますます増えるにつれて、将来的には NAND Flash のフロントエンドの集積も、元の NAND アレイ(Array)+CMOS 回路層の積層から、NAND アレイ + NAND アレイ + CMOS 回路層の積層に転換するため、さらに多くの「ハイブリッドボンディング」のニーズが生まれる。

まとめると、3D NAND メーカーにとって、400 層以上の NAND 積層を発展させるには、ハイブリッドボンディング技術は既に重要な核心技術となっている。

YMTCが技術的な優位性を築いている

CBA アーキテクチャに率先して転換した 3D NAND メーカーとして、YMTCは 2018 年に独自開発の Xtacking 技術を発表して以来、CBA アーキテクチャの方向で多くの投資を行ってきた。2021 年、YMTCは Xperi と DBI ハイブリッドボンディング技術などの関連特許ポートフォリオのライセンス契約を締結した。これらの積極的な投資が、YMTCが数年間で急速に NAND Flash 技術面で国際一流メーカーに追いつくことができた鍵となっている。

現在、YMTCが独自開発した Xtacking 技術はすでに 4.x バージョンまで進歩しており、160 層、192 層、232 層の製品も量産に成功している。最新の調査報告によると、YMTCは今年の初めに、2yy(推定 270 層)の 3D TLC(3 レベルセル)NAND の商業化にも成功している。

現在、上位の 3D NAND 大手メーカーはすべて 200 層以上の 3D NAND を量産しており、積極的に 300 層の 3D NAND の量産を進めており、さらに 400 層以上に向けて進出している。例えば、2024 年 11 月、SK ハイニックス(SK Hynix)は世界最高の 321 層の 3D NAND の量産を開始すると発表した。その後、サムスン(Samsung)も国際固体回路会議(ISSCC)で 400 層を超える新しい 3D NAND を展示し、インターフェース速度は 5.6 GT/s であると発表した。しかし、YMTCの 2yy 3D NAND は、現在商用化されている 3D NAND 製品の中で、依然として積層数が最も高く、記憶密度も最も高いものだ。

TechInsights は、「YMTCの 2yy 3D NAND は、私たちが市場で見つけた中で最も密度の高い NAND である」と述べ、「最も重要なことは、業界で初めて 20Gb/mm² を超えるビット密度を達成した 3D NAND である」と評価した。

明らかに、YMTCは近年、外部からの様々な制限に直面しているものの、依然として独自開発の Xtacking 技術により、業界のリード位置にある。その鍵は、YMTCが率先して CBA アーキテクチャに転換し、ハイブリッドボンディング技術の歩留まりを安定させたことにある。この過程で、YMTCは Xperi のハイブリッドボンディング技術を基に、独自開発のハイブリッドボンディング技術やその他の 3D NAND 製造技術の特許をたくさん蓄積している。

なお、2023 年 11 月、YMTCは米国で 3D NAND チップの大手メーカーに対して、8 つの 3D NAND 特許を侵害したと訴えた。その後、2024 年 7 月、YMTCは米国でマイクロン(Micron)に対して 11 の特許を侵害したと訴えた。これも、YMTCが近年、3D NAND 分野で蓄積した豊富な技術特許を側面から浮き彫りにしている。

大手メーカーの CBA アーキテクチャへの転換が遅れている

サムスン、SK ハイニックスなどの従来の 3D NAND 大手メーカーにとって、従来の単一ウェハ生産においては大きな技術的な優位性と生産能力の優位性を持っている。しかし、従来の単一ウェハ生産から CBA アーキテクチャの 2 枚のウェハ生産に転換するには、新しいクリーンルームスペースと設備に対する追加投資が不可避であり、同時にハイブリッドボンディング技術による歩留まりのチャレンジに直面することになる。このため、彼らは CBA アーキテクチャに転換する意欲があまり積極的ではない。

東芝セミコンから独立したキオクシア(Kioxia)は、YMTCに次いで、CBA アーキテクチャ技術を採用して 3D NAND 製品を大量生産する主要なメーカーの 1 つであるが、彼らの CBA アーキテクチャに基づく第 8 世代技術(BiCS8)の 218 層 3D NAND は、2024 年の後半になって初めて量産された。

SK ハイニックスとマイクロンは、それぞれ 2020 年と 2022 年に Xperi(子会社 Adeia)からハイブリッドボンディング技術のライセンスを取得している。しかし、SK ハイニックスとマイクロンは、2025 年に CBA アーキテクチャに基づく 300 層以上の 3D NAND の量産を計画しており、サムスンは 2026 年(最速で 2025 年末)に CBA アーキテクチャに基づく第 10 世代で 400 層を超える積層数の V-NAND の量産を計画している。

TechInsights の Jeongdong Choi 博士は最近、記者のインタビューに応じて、「YMTCがこのように短い期間で 160 層と 232 層を実現したことは驚くべきことだ。設備調達の制限にもかかわらず、エッチング、ALD(原子層堆積)プロセスと反り防止プロセスがうまく最適化されているようだ」と述べた。

これに比べて、「サムスンは V10 から三重スタックを採用し、合計で 2 枚のウェハを使用するハイブリッドボンディングを行う。プロセス転換や新設備投資など、多くの変化があるため、製造コストは必然的に長期間ハイブリッドボンディングを使用してきたYMTCよりもはるかに高くなる」と Jeongdong Choi 氏は説明した。

回避が難しい特許壁

正に、サムスン(Samsung)、SK ハイニックス(SK Hynix)などの大手メーカーが CBA アーキテクチャへの転換が遅れている為、既にCBA アーキテクチャに基づく 3D NANDとハイブリッドボンディング技術に長年の継続投資を行っているYMTCを直面する際に、必然的に特許の壁にぶつかるだろう。

資料によると、現在ハイブリッドボンディング技術の特許は主に Xperi、YMTCと台積電(TSMC)が握っている。しかし、Xperi という会社は主に技術ライセンスを行っており、TSMCも主に論理チップの製造を行っている。明らかに、YMTCが 3D NAND の研究開発と製造の過程で蓄積したハイブリッドボンディング技術の特許は、他の 3D NAND メーカーにとって、回避することができるかどうかは大きな課題となる。

ZDNet Korea の報道によると、複数の関係者は、サムスンがYMTCと「ハイブリッドボンディング」技術の特許ライセンス契約を締結したのは、サムスンが「次世代の NAND Flash である V10、V11、V12 などを開発するには、YMTCの特許を回避することはほとんど不可能だ」と判断したからだと述べている。

サムスンの計画によると、同社は最速で今年の年末までに V10 の量産を開始することを目指しており、そのためには関連する特許問題をできるだけ早く解決する必要がある。

そのため、サムスンがYMTCとハイブリッドボンディング特許に関するライセンス契約を締結したという動きは、友好的な協力を通じて技術開発を加速するための戦略と見られる。ただし、サムスンが Xperi などの他の会社からも特許ライセンスを取得しているかどうかは、現在まだ不明だ。

YMTCにとって、今回、サムスンのようなトップレベルのメモリ技術大手に特許ライセンスを提供することは、中国のメモリ産業の歴史上初めてのことであり、YMTCが 3D NAND 分野における技術革新の実力を十分に際立たせている。

なお、サムスンからの認可を得た後、まだ CBA アーキテクチャ製品を量産していない SK ハイニックスなどの 3D NAND メーカーが、これからYMTCから「ハイブリッドボンディング」の特許ライセンスを取得することを模索する可能性もある。