6月18日、ファンアウト・パネルレベルパッケージ「FOPLP(Fan Out Panel Level Package)」は次世代の先進的なパッケージングの重要な方向として注目されているため、インテルやサムスンなどの海外大手ウェハー企業に加え、中国台湾のファウンドリ大手TSMC、ASE、メモリ封測リーダーのPowertech Technology Inc.(PTI)などの大手企業も積極的に展開を進め、NVIDIAやAMDなどの大手メーカーのHPC/AIチップ向け先進パッケージングのビジネスチャンスを狙っている。

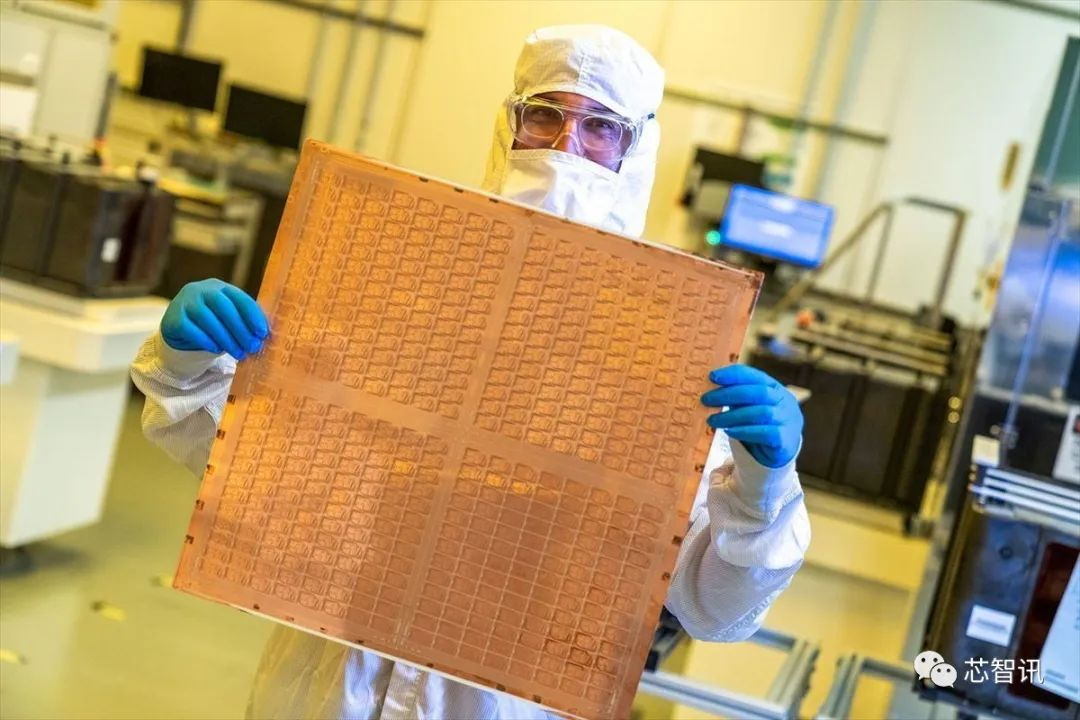

情報によると、TSMCの関連技術は「CoPoS(Chip-on-Panel-on-Substrate)」と呼ばれ、工場は中国台湾省・嘉義市に置かれ、2026年の試験ライン設置が予定されている。ASEは中国台湾省・高雄市ですでに量産可能な「300x300mm」のパネルレベルパッケージング・ラインを有している。PTIは最も早くから取り組んでおり、2019年に量産を実現し、「PiFO(Pillar integration FO)」と命名されている。

業界分析によると、高性能コンピューティングチップの高集積技術にはそれぞれ強みがある。パネルレベルファンアウトパッケージングはウェハーと比べ、基板面積が大きくて異種統合が可能で、5G通信フィルター機能を搭載した回路設計を統合でき、チップの性能と機能が大幅に向上する。このため、5G通信やIoTデバイスなど多様な製品に適しており、様々な民生用電子機器のさらなる小型化に貢献できるという。

TSMCのCoPoS技術は主にAIと高速コンピューティング(HPC)アプリケーションに焦点を当てており、2028年に量産化される予定と噂されている。このプロセスは、CoWoSを「パネル化」し正方形設計に転換したもので、チップの生産量拡大に有利だという。TSMCはこの前北米技術フォーラムで最新のA14プロセスを発表し、2027年にフォトマスクサイズの9.5倍の新CoWoS技術を量産する計画も示した。これにより、より多くのロジックチップとメモリチップを1つのパッケージに統合でき、業界ではこのトレンドもCoPoSの発展と合致すると見られている。ASEはすでに量産可能な300x300mmのパネルレベルパッケージング・ライン(FanOutプロセス採用)を有している。PTIも自社のファンアウト・パネルレベルパッケージング技術を「PiFO」と命名しており、CoPoSに類似している技術だという。

(原文:https://www.icsmart.cn/93139/)